DC/DC基本原理9 (Buck Converter) : FB 回授電路 -基本原理、電阻選值影響、FB佈線原則

I. 基本原理

首先認識FB電壓回授電路之前,必須先知道什麼是回授系統 Feedback (FB) System,回授系統的處理部分可以是電氣或電子的,範圍從非常簡單到高度複雜的電路。簡單的類比回授控制電路可以使用單獨或分立的元件(例如電晶體、電阻器和電容器等)構建,或使用基於微處理器的積體電路(IC)來構建更複雜的數位回授系統。

正如我們所看到的,開環系統是開放式系統,並且不會嘗試補償由於電路參數(例如增益和穩定性、溫度、電源電壓)變化而導致的電路條件變化或負載條件變化和/或外部幹擾。但透過引入回饋可以消除或至少大大減少這些「開環」變化的影響。反饋系統是一種對輸出訊號進行採樣,然後反饋到輸入以形成驅動系統的誤差訊號的系統。

雖然控制系統有許多不同類型,但回授控制主要有兩種類型:正回授和負回授控制,如圖1所示。

1.正回授系統

在“正回授控制系統”中,由於回授與輸入“同相”,因此控制器將設定點和輸出值相加。正(或再生)回授的作用是「增加」系統增益,即應用正回授的總增益將大於沒有回授的增益。例如,如果有人讚揚你或對某件事給予你正面的回饋,你就會對自己感到高興並且充滿活力,你會感覺更正面。然而,在電子和控制系統中,過多的讚揚和正回授可能會使系統增益增加太多,這會導致振盪電路響應,因為它會增加有效輸入訊號的振幅。

2.負回授系統

在“負回授控制系統”中,由於回授與原始輸入“異相”,因此設定點和輸出值會相互減去。負(或退化)回饋的作用是「減少」增益。例如,如果有人批評你或給你關於某事的負面回饋,你就會對自己感到不高興,因此缺乏能量,你會感覺不那麼正面。由於負回授會產生穩定的電路響應,提高穩定性並增加給定系統的工作頻寬,因此大多數控制和回授系統都是退化的,從而減少了增益的影響。

負回授在放大器和控制系統中的使用很廣泛,因為通常負回授系統比正回授系統更穩定。

在DC/DC Converter輸出電壓設定,常用的方法會使用FB分壓電阻來調整輸出電壓,其原理就如同上述所說的負回授控制系統,透過FB電路回授輸出電壓至IC內部的控制系統。

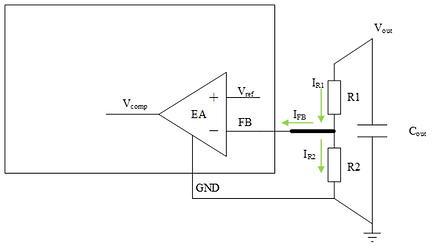

FB電路是由兩個電阻(R1、R2)串聯所構成,如圖2所示,其中R1會連接Vout端,R2則連接至GND,而誤差放大器的FB Pin 則連接在兩電阻之間。

因此FB Pin上的電壓就可由式(1)所表示,可得知FB Pin上的電壓會經由FB兩個分壓電阻的數值比例而改變。

II. FB電阻選值影響

由上文我們知道了FB回授電路會因為FB電阻的比例選擇,藉此改變輸出電壓,然而電阻的選值可以選很大亦或是可以選很小嗎? 因此,第二節會討論FB電路上的電阻選值會造成什麼影響。

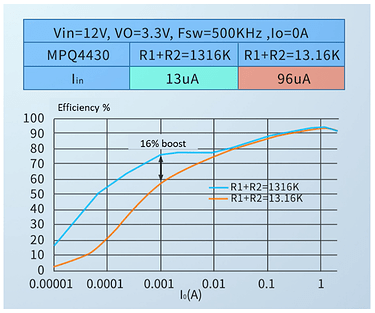

以MPQ4430為例,圖3表示具有低靜態電流(IQ) 的DC/DC 變換器,其FB 分壓電阻在不同量級下帶來的效率差異。

DC/DC待機時Error Amplifier也是在工作的,只是此時沒有負載,如果器件經常處於待機狀態,那麼就需要考慮如何減小待機功耗,如果器件工作時間居多,待機功耗可以忽略不計。

經由比較兩組阻值,R1+R2=1316kΩ 以及 R1+R2=13.16kΩ,第一組阻值比第二組大一百倍,再觀察Iin輸入電流,第一組選擇較大的阻值其Iin電流為13uA,而第二組選擇較小的阻值其其Iin電流為96uA;經由比較可得知,對於待機功耗可選用較大的FB分壓電阻的選值,降低待機功耗的耗損,進而提升待機時的效率。

圖3:R1 和R2 不同量級帶來的效率差異 (From MPS)

對低功耗DC/DC來說,典型的電阻式反饋設計一般要求上分壓電阻R1+下分壓電阻R2具有非常大的總電阻,經驗式為R1+R2≈1MΩ,因為這樣可以最小化流過回授分壓電阻的電流。在含電池或者對能效有要求的設備中,我們可以適當增大FB分壓電阻阻值來減小設備待機功耗。

(2)輸出電壓精度

根據上文所述,增大FB 分壓電阻的阻值,可以降低待機功耗,但是分壓電阻真的選的越大越好嗎? 實際情況是,選擇的分壓電阻過大,反而會影響DC/DC的輸出電壓精度。

FB 是運算放大器的負輸入端,它會汲取一定的電流,如圖4所示。當FB 電流(IFB)在分壓網絡中佔比較小時,IFB 可忽略不計,當其占比較大,IFB 就不容忽視,會影響輸出電壓的精準度。

流入回授電路電流IR1,而IR1等於IR2+IFB,其中IR1電流會隨著R1和R2的值增加而減小,假設反饋電流IFB固定不變時,當R1和R2的阻值增加、IR1回授電流減少,因此IFB電流相對於IR1的百分占比就變更大了,並且IR2降低,從而產生低於預期的反饋引腳電壓VFB,當實際輸出電壓(VOUT) 由於IFB 的存在而超過預設值時,會降低電壓精度,如式(3)表示。

因此實際調控出來的輸出電壓與期望輸出電壓會有落差,如果當分壓電阻取值太大時,反而會影響輸出電壓的精準度。

如果反饋電流IFB相對占比很小時,因此可忽略不計,其可由式(4)表示。

我們將VFB同內部基準電壓Vref比較以此來輸出電壓,反饋電壓的任何一點誤差都會導致輸出電壓不精確。但是IFB在實際系統中並非固定不變,不同的器件均不相同,並且也隨工作狀態而變化。要想估算出漏電流引起的輸出電壓極端變化情況,需要在計算中使用IFB的最大規定值。

因此,建議選擇合適的阻值,使流經分壓電阻的電流IR1超過IFB 的50 倍。

(3)補償器增益

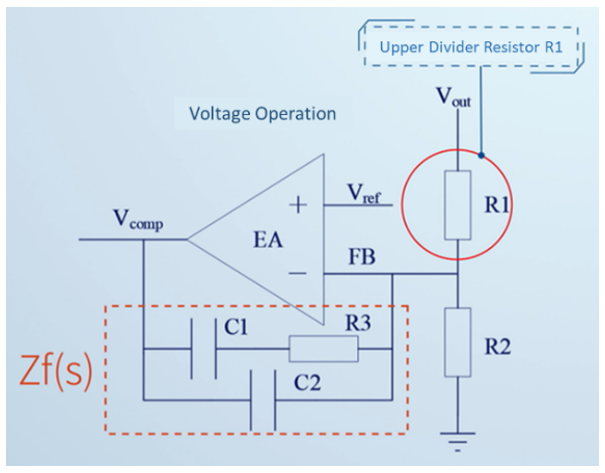

FB 電阻還會影響IC內部的環路特性。當反饋網路只是單電阻的情況時,電壓型運算放大器,誤差放大器增益與上分壓電阻R1 有關,在動態負載對紋波有要求的場景,我們可以調整R1 阻值做進一步優化,圖5所示為電壓模式運算放大器架構。

圖5: 電壓模式運算放大器架構 (From MPS)

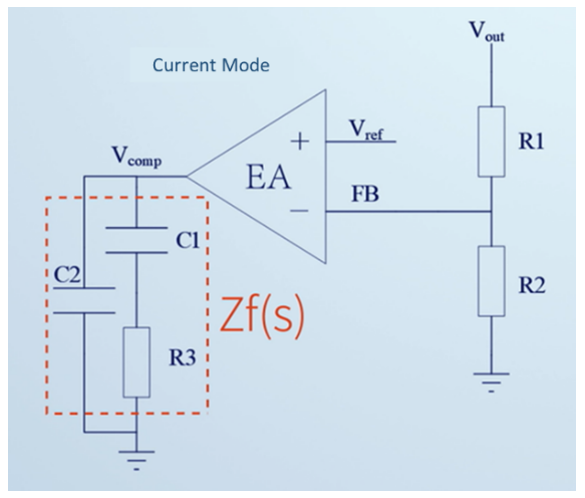

在電流型運算放大器中,運放增益(GEA(S)) 與R1 / R2 值沒有直接關係,但與兩個電阻的比值有關,圖6 所示為電流模式運算放大器架構。

圖6:電流模式運算放大器架構 (From MPS)

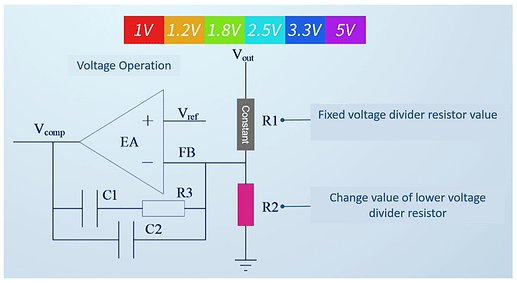

對於不同的VOUT 場景(1V、1.2V、1.8V、2.5V、3.3V 或5V),電壓型運算放大器建議保持上分壓電阻的阻值不變,只調節下分壓電阻的阻值,以獲得近似的環路特性,如圖7所示。

圖7:根據輸出電壓的不同調整下分壓電阻的阻值 (From MPS)

III. FB佈線原則

確定FB 分壓電阻值後,還需要注意FB 引腳的接線,FB 是容易耦合噪聲的高阻抗引腳,可以見下述幾種FB線路的應用。

一旦確定了用於反饋(FB)的分壓電阻值,還需要注意FB 引腳的連接方式,因為FB 引腳是一個容易耦合噪聲的高阻抗引腳。FB 引腳的正確連接和保護措施是確保穩定輸出的關鍵,適當的過濾和線路佈局可以幫助減少噪聲的影響,確保電路能夠正確運作,幾種FB線路的應用如下述所表示:

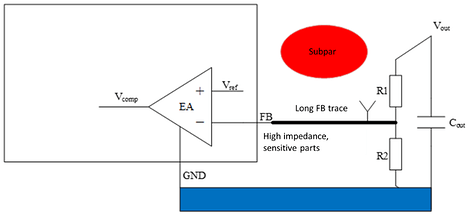

(1) R1、R2會擺放在輸出電容附近(FB走線長)

這樣的佈局可能導致FB線路較長,且在電路中扮演了一種天線的角色,這會增加耦合到FB線路的外部干擾,這樣的外部干擾可能會引起虛偽的反饋信號,導致輸出電壓的不穩定或變化,如圖8所示。

解決方法: 優化線路佈局,使FB線路盡量縮短,減少其充當天線的長度,這可以幫助減少外部干擾的耦合。

圖8:FB 走線長-易耦合非實反饋 (From MPS)

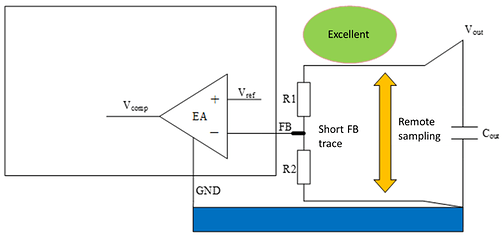

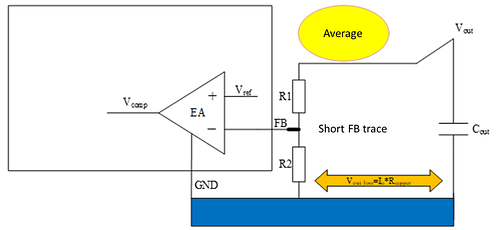

(2)R1、R2擺放在IC 的FB 引腳附近 (FB 走線短)

Vout輸出直流電平其抗干擾能力強,所以可採用長走線,如圖9所示,相較於第(1)種方式,FB是敏感的回授訊號,其線路走線過長容易受到外部的干擾。因此FB走線應靠近IC的FB引腳,使得FB走線越短越好。

圖9:FB 走線短-靠近IC (From MPS)

(3)R1、R2擺放在IC 的FB 引腳附近 (Remote Sensing)

一般在輸出電流(IOUT)只有幾個安培時,R2 的接地可以靠近芯片地,但當IOUT 超過10A 時,由於接地線上的敷銅有限,地線上的電壓會損失,導致實際VOUT 低於預設電壓;在這種情況下,建議使用遠程採樣(Remote Sensing),如圖10所示。

圖10:FB 走線短-遠程採樣 (From MPS)

留言

張貼留言